# ATmega16U4/ATmega32U4

# **Atmel**

# 8-bit Microcontroller with 16/32K bytes of ISP Flash and USB Controller

# DATASHEET SUMMARY

# **Features**

- High Performance, Low Power AVR® 8-Bit Microcontroller

- Advanced RISC Architecture

- 135 Powerful Instructions Most Single Clock Cycle Execution

- 32 x 8 General Purpose Working Registers

- Fully Static Operation

- Up to 16 MIPS Throughput at 16MHz

- On-Chip 2-cycle Multiplier

- Non-volatile Program and Data Memories

- 16/32KB of In-System Self-Programmable Flash

- 1.25/2.5KB Internal SRAM

- 512Bytes/1KB Internal EEPROM

- Write/Erase Cycles: 10,000 Flash/100,000 EEPROM

- Data retention: 20 years at 85°C/ 100 years at 25°C<sup>(1)</sup>

- Optional Boot Code Section with Independent Lock Bits

In-System Programming by On-chip Boot Program

True Read-While-Write Operation

Parts using external XTAL clock are pre-programed with a default USB bootloader

- Programming Lock for Software Security

- JTAG (IEEE<sup>®</sup> std. 1149.1 compliant) Interface

- Boundary-scan Capabilities According to the JTAG Standard

- Extensive On-chip Debug Support

- Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface

- USB 2.0 Full-speed/Low Speed Device Module with Interrupt on Transfer Completion

- Complies fully with Universal Serial Bus Specification Rev 2.0

- Supports data transfer rates up to 12Mbit/s and 1.5Mbit/s

- Endpoint 0 for Control Transfers: up to 64-bytes

- Six Programmable Endpoints with IN or Out Directions and with Bulk, Interrupt or Isochronous Transfers

- Configurable Endpoints size up to 256 bytes in double bank mode

- Fully independent 832 bytes USB DPRAM for endpoint memory allocation

- Suspend/Resume Interrupts

- CPU Reset possible on USB Bus Reset detection

- 48MHz from PLL for Full-speed Bus Operation

- USB Bus Connection/Disconnection on Microcontroller Request

- Crystal-less operation for Low Speed mode

- Peripheral Features

- On-chip PLL for USB and High Speed Timer: 32 up to 96MHz operation

- One 8-bit Timer/Counter with Separate Prescaler and Compare Mode

- Two 16-bit Timer/Counter with Separate Prescaler, Compare- and Capture Mode

- One 10-bit High-Speed Timer/Counter with PLL (64MHz) and Compare Mode

- Four 8-bit PWM Channels

- Four PWM Channels with Programmable Resolution from 2 to 16 Bits

- Six PWM Channels for High Speed Operation, with Programmable Resolution from 2 to 11 Bits

- Output Compare Modulator

- 12-channels, 10-bit ADC (features Differential Channels with Programmable Gain)

- Programmable Serial USART with Hardware Flow Control

- Master/Slave SPI Serial Interface

- Byte Oriented 2-wire Serial Interface

- Programmable Watchdog Timer with Separate On-chip Oscillator

- On-chip Analog Comparator

- Interrupt and Wake-up on Pin Change

- On-chip Temperature Sensor

- Special Microcontroller Features

- Power-on Reset and Programmable Brown-out Detection

- Internal 8MHz Calibrated Oscillator

- Internal clock prescaler and On-the-fly Clock Switching (Int RC / Ext Osc)

- External and Internal Interrupt Sources

- Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby, and Extended Standby

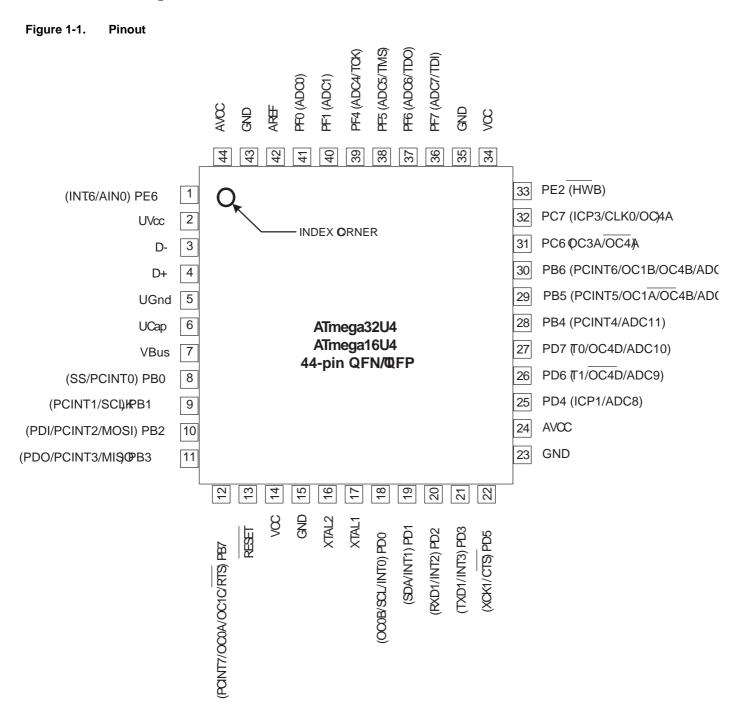

- I/O and Packages

- All I/O combine CMOS outputs and LVTTL inputs

- 26 Programmable I/O Lines

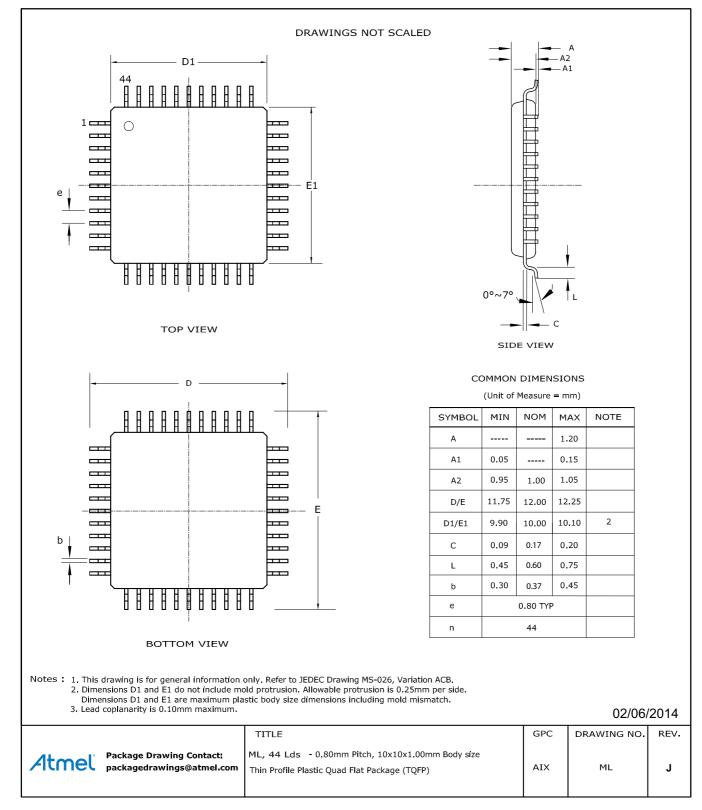

- 44-lead TQFP Package, 10x10mm

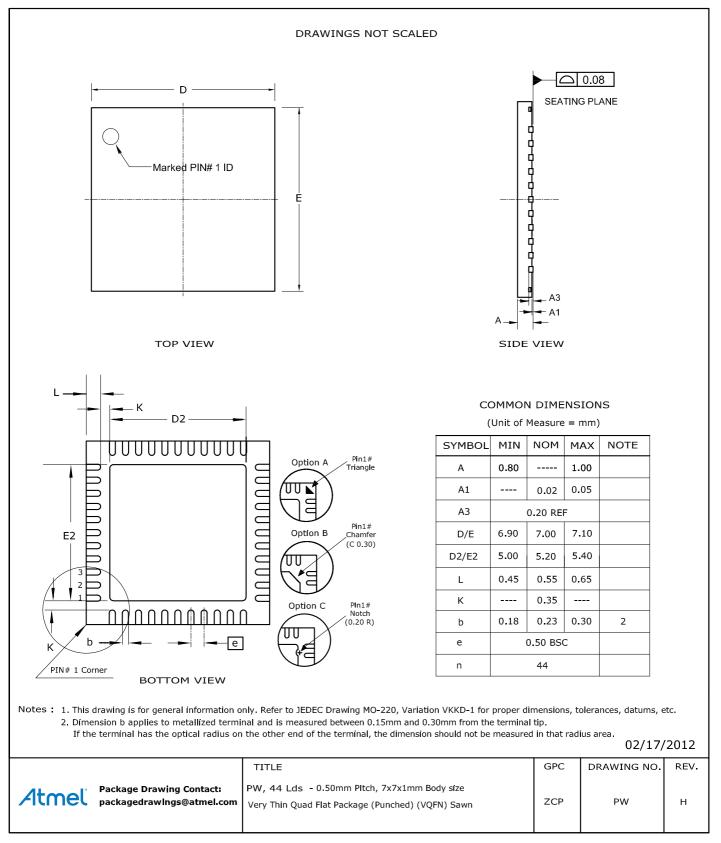

- 44-lead QFN Package, 7x7mm

- Operating Voltages

- 2.7 5.5V

- Operating temperature

- Industrial (-40°C to +85°C)

- Maximum Frequency

- 8MHz at 2.7V Industrial range

- 16MHz at 4.5V Industrial range

- Note: 1. See "Data Retention" on page 8 for details.

# 1. Pin Configurations

# 2. Overview

The ATmega16U4/ATmega32U4 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the device achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

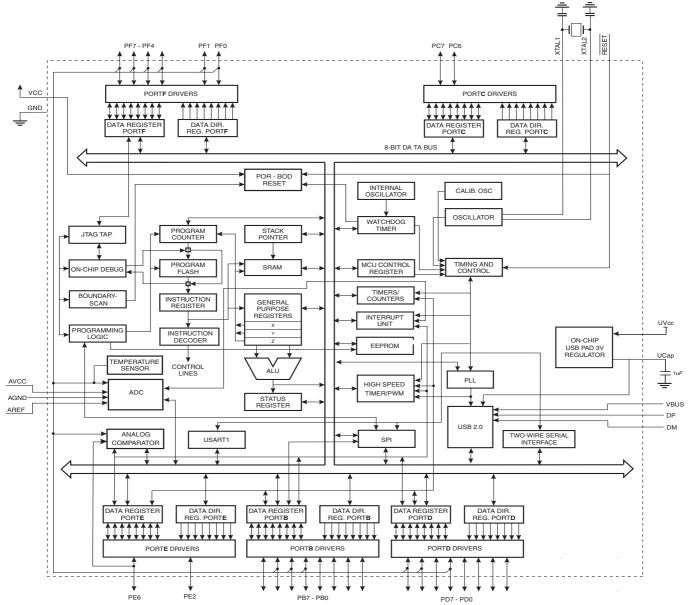

# 2.1 Block Diagram

Figure 2-1. Block Diagram

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The device provides the following features: 16/32K bytes of In-System Programmable Flash with Read-While-Write capabilities, 512Bytes/1K bytes EEPROM, 1.25/2.5K bytes SRAM, 26 general purpose I/O lines (CMOS outputs and LVTTL inputs), 32 general purpose working registers, four flexible Timer/Counters with compare modes and PWM, one more high-speed Timer/Counter with compare modes and PLL adjustable source, one USART (including CTS/RTS flow control signals), a byte oriented 2-wire Serial Interface, a 12-channels 10-bit ADC with optional differential input stage with programmable gain, an on-chip calibrated temperature sensor, a programmable Watchdog Timer with Internal Oscillator, an SPI serial port, IEEE std. 1149.1 compliant JTAG test interface, also used for accessing the On-chip Debug system and programming and six software selectable

power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or Hardware Reset. The ADC Noise Reduction mode stops the CPU and all I/O modules except ADC, to minimize switching noise during ADC conversions. In Standby mode, the Crystal/Resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low power consumption.

The device is manufactured using the Atmel<sup>®</sup> high-density nonvolatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an On-chip Boot program running on the AVR core. The boot program can use any interface to download the application program in the application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the device is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The ATmega16U4/ATmega32U4 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.

# 2.2 Pin Descriptions

#### 2.2.1 VCC

Digital supply voltage.

# 2.2.2 GND

Ground.

# 2.2.3 Port B (PB7..PB0)

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port B has better driving capabilities than the other ports.

Port B also serves the functions of various special features of the device as listed on page 74.

# 2.2.4 Port C (PC7,PC6)

Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tristated when a reset condition becomes active, even if the clock is not running.

Only bits 6 and 7 are present on the product pinout.

Port C also serves the functions of special features of the device as listed on page 77.

# 2.2.5 Port D (PD7..PD0)

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port D also serves the functions of various special features of the ATmega16U4/ATmega32U4 as listed on page 78.

#### 2.2.6 Port E (PE6,PE2)

Port E is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port E output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port E pins that are externally pulled low will source current if the pull-up resistors are activated. The Port E pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Only bits 2 and 6 are present on the product pinout.

Port E also serves the functions of various special features of the ATmega16U4/ATmega32U4 as listed on page 81.

#### 2.2.7 Port F (PF7..PF4, PF1,PF0)

Port F serves as analog inputs to the A/D Converter.

Port F also serves as an 8-bit bi-directional I/O port, if the A/D Converter channels are not used. Port pins can provide internal pull-up resistors (selected for each bit). The Port F output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port F pins that are externally pulled low will source current if the pull-up resistors are activated. The Port F pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Bits 2 and 3 are not present on the product pinout.

Port F also serves the functions of the JTAG interface. If the JTAG interface is enabled, the pull-up resistors on pins PF7(TDI), PF5(TMS), and PF4(TCK) will be activated even if a reset occurs.

#### 2.2.8 D-

USB Full speed / Low Speed Negative Data Upstream Port. Should be connected to the USB D- connector pin with a serial  $22\Omega$  resistor.

#### 2.2.9 D+

USB Full speed / Low Speed Positive Data Upstream Port. Should be connected to the USB D+ connector pin with a serial  $22\Omega$  resistor.

#### 2.2.10 UGND

USB Pads Ground.

#### 2.2.11 UVCC

USB Pads Internal Regulator Input supply voltage.

# 2.2.12 UCAP

USB Pads Internal Regulator Output supply voltage. Should be connected to an external capacitor (1µF).

#### 2.2.13 VBUS

USB VBUS monitor input.

# 2.2.14 RESET

Reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in Table 8-2 on page 53. Shorter pulses are not guaranteed to generate a reset.

#### 2.2.15 XTAL1

Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

#### 2.2.16 XTAL2

Output from the inverting Oscillator amplifier.

#### 2.2.17 AVCC

AVCC is the supply voltage pin (input) for all the A/D Converter channels. If the ADC is not used, it should be externally connected to  $V_{CC}$ . If the ADC is used, it should be connected to  $V_{CC}$  through a low-pass filter.

#### 2.2.18 AREF

This is the analog reference pin (input) for the A/D Converter.

# 3. About

# 3.1 Disclaimer

Typical values contained in this datasheet are based on simulations and characterization of other AVR microcontrollers manufactured on the same process technology. Min. and Max. values will be available after the device is characterized.

# 3.2 Resources

A comprehensive set of development tools, application notes and datasheets are available for download on http://www.atmel.com/avr.

# 3.3 Code Examples

This documentation contains simple code examples that briefly show how to use various parts of the device. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Confirm with the C compiler documentation for more details.

These code examples assume that the part specific header file is included before compilation. For I/O registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

# 3.4 Data Retention

Reliability Qualification results show that the projected data retention failure rate is much less than 1PPM over 20 years at 85°C or 100 years at 25°C.

# 4. Register Summary

| Address          | Name            | Bit 7    | Bit 6    | Bit 5     | Bit 4                                  | Bit 3            | Bit 2          | Bit 1                              | Bit 0           | Page |

|------------------|-----------------|----------|----------|-----------|----------------------------------------|------------------|----------------|------------------------------------|-----------------|------|

| (0xFF)           | Reserved        | -        | -        | -         | -                                      | -                | -              | -                                  | -               | U    |

| (0xFE)           | Reserved        | -        | -        | -         | -                                      | -                | -              | -                                  | -               |      |

| (0xFD)           | Reserved        | -        | -        | -         | -                                      | -                | -              | -                                  | -               |      |

| (0xFC)           | Reserved        | -        | -        | -         | -                                      | -                | -              | -                                  | -               |      |

| (0xFB)           | Reserved        | -        | -        | -         | -                                      | -                | -              | -                                  | -               |      |

| (0xFA)           | Reserved        | -        | -        | -         | -                                      | -                | -              | -                                  | -               |      |

| (0xF9)           | Reserved        |          | -        | -         |                                        |                  |                | -                                  | -               |      |

| (0xF8)           | Reserved        | -        | -        | -         | -                                      | -                | -              | -                                  | -               |      |

| (0xF7)           | Reserved        | -        | -        | -         | -                                      | -                | -              | -                                  | -               |      |

| (0xF6)           | Reserved        | -        | -        | -         | -                                      | -                | -              | -                                  | -               |      |

| (0xF5)           | Reserved        | -        | -        | -         | -                                      | -<br>EPINT6:0    | -              | -                                  | -               |      |

| (0xF4)<br>(0xF3) | UEINT<br>UEBCHX | -        | -        | -         |                                        | EPIN16:0<br>-    |                | BYCT10:8                           |                 |      |

| (0xF2)           | UEBCLX          | -        | -        | -         | -<br>BV                                | -<br>CT7:0       |                | BICTIU.8                           |                 |      |

| (0xF1)           | UEDATX          |          |          |           |                                        | T7:0             |                |                                    |                 |      |

| (0xF0)           | UEIENX          | FLERRE   | NAKINE   | -         | NAKOUTE                                | RXSTPE           | RXOUTE         | STALLEDE                           | TXINE           |      |

| (0xEF)           | UESTA1X         | -        | -        | -         | -                                      | -                | CTRLDIR        |                                    | RBK1:0          |      |

| (0xEE)           | UESTA0X         | CFGOK    | OVERFI   | UNDERFI   | -                                      | DTSE             | EQ1:0          |                                    | YBK1:0          |      |

| (0xED)           | UECFG1X         |          | -        | EPSIZE2:0 | I                                      |                  | K1:0           | ALLOC                              | -               |      |

| (0xEC)           | UECFG0X         | EPTY     | PE1:0    | -         | -                                      | -                | -              | -                                  | EPDIR           |      |

| (0xEB)           | UECONX          | -        | -        | STALLRQ   | STALLRQC                               | RSTDT            | -              | -                                  | EPEN            |      |

| (0xEA)           | UERST           | -        |          |           |                                        | EPRST6:0         |                |                                    |                 |      |

| (0xE9)           | UENUM           | -        | -        | -         | -                                      | -                |                | EPNUM2:0                           |                 |      |

| (0xE8)           | UEINTX          | FIFOCON  | NAKINI   | RWAL      | NAKOUTI                                | RXSTPI           | RXOUTI         | STALLEDI                           | TXINI           |      |

| (0xE7)           | Reserved        |          |          | -         | -                                      | -                | -              |                                    |                 |      |

| (0xE6)           | UDMFN           | -        | -        | -         | FNCERR                                 | -                | -              | -                                  | -               |      |

| (0xE5)           | UDFNUMH         | -        | -        | -         | -                                      | -                |                | FNUM10:8                           |                 |      |

| (0xE4)           | UDFNUML         |          | n        |           | FNI                                    | JM7:0            |                |                                    |                 |      |

| (0xE3)           | UDADDR          | ADDEN    |          |           |                                        | UADD6:0          |                |                                    | 0.1075          |      |

| (0xE2)           | UDIEN           | -        | UPRSME   | EORSME    | WAKEUPE                                | EORSTE           | SOFE           | MSOFE                              | SUSPE           |      |

| (0xE1)<br>(0xE0) | UDINT<br>UDCON  | -        | UPRSMI   | EORSMI    | WAKEUPI                                | EORSTI<br>RSTCPU | SOFI<br>LSM    | MSOFI<br>RMWKUP                    | SUSPI<br>DETACH |      |

| (0xDF)           | Reserved        | -        | -        | -         | -                                      | Ratero           | LOIVI          | RIVIVINOF                          | DETACH          |      |

| (0xDE)           | Reserved        |          |          |           |                                        |                  |                |                                    |                 |      |

| (0xDD)           | Reserved        |          |          |           |                                        |                  |                |                                    |                 |      |

| (0xDC)           | Reserved        |          |          |           |                                        |                  |                |                                    |                 |      |

| (0xDB)           | Reserved        |          |          |           |                                        |                  |                |                                    |                 |      |

| (0xDA)           | USBINT          | -        | -        | -         | -                                      | -                | -              | -                                  | VBUSTI          |      |

| (0xD9)           | USBSTA          | -        | -        | -         | -                                      | -                | -              | ID                                 | VBUS            |      |

| (0xD8)           | USBCON          | USBE     | -        | FRZCLK    | OTGPADE                                | -                | -              | -                                  | VBUSTE          |      |

| (0xD7)           | UHWCON          | -        | -        | -         | -                                      | -                | -              | -                                  | UVREGE          |      |

| (0xD6)           | Reserved        |          |          |           |                                        |                  |                |                                    |                 |      |

| (0xD5)           | Reserved        |          |          |           |                                        |                  |                |                                    |                 |      |

| (0xD4)           | DT4             | DT4H3    | DT4H2    | DT4H1     | DT4H0                                  | DT4L3            | DT4L2          | DT4L1                              | DT4L0           |      |

| (0xD3)           | Reserved        |          |          |           |                                        | F                | inter D        |                                    |                 |      |

| (0xD2)           | OCR4D           |          |          |           | er/Counter4 - Out                      |                  |                |                                    |                 |      |

| (0xD1)           | OCR4C           |          |          |           | er/Counter4 - Out                      |                  |                |                                    |                 |      |

| (0xD0)<br>(0xCF) | OCR4B<br>OCR4A  |          |          |           | er/Counter4 - Out<br>er/Counter4 - Out |                  |                |                                    |                 |      |

| (0xCF)<br>(0xCE) | UDR1            |          |          | TIME      |                                        | Data Register    |                |                                    |                 |      |

| (0xCE)<br>(0xCD) | UBRR1H          | -        | -        | -         | - USARTTI/C                            |                  | SART1 Baud Pat | te Register High E                 | Byte            |      |

| (0xCC)           | UBRR1L          |          | 1        |           | -<br>JSART1 Baud Ra                    |                  |                |                                    | . , .~          |      |

| (0xCB)           | UCSR1D          | -        | -        | -         | -                                      | -                | -              | CTSEN                              | RTSEN           |      |

| (0xCA)           | UCSR1C          | UMSEL11  | UMSEL10  | UPM11     | UPM10                                  | USBS1            | UCSZ11         | UCSZ10                             | UCPOL1          |      |

| (0xC9)           | UCSR1B          | RXCIE1   | TXCIE1   | UDRIE1    | RXEN1                                  | TXEN1            | UCSZ12         | RXB81                              | TXB81           |      |

| (0xC8)           | UCSR1A          | RXC1     | TXC1     | UDRE1     | FE1                                    | DOR1             | PE1            | U2X1                               | MPCM1           |      |

| (0xC7)           | CLKSTA          | -        | -        | -         | -                                      | -                | -              | RCON                               | EXTON           |      |

| (0xC6)           | CLKSEL1         | RCCKSEL3 | RCCKSEL2 | RCCKSEL1  | RCCKSEL0                               | EXCKSEL3         | EXCKSEL2       | EXCKSEL1                           | EXCKSEL0        |      |

| (0xC5)           | CLKSEL0         | RCSUT1   | RCSUT0   | EXSUT1    | EXSUT0                                 | RCE              | EXTE           | -                                  | CLKS            |      |

| (0xC4)           | TCCR4E          | TLOCK4   | ENHC4    | OC4OE5    | OC4OE4                                 | OC4OE3           | OC4OE2         | OC4OE1                             | OC4OE0          |      |

| (0xC3)           | TCCR4D          | FPIE4    | FPEN4    | FPNC4     | FPES4                                  | FPAC4            | FPF4           | WGM41                              | WGM40           |      |

|                  |                 | COM4A1S  | COM4A0S  | COM4B1S   | COM4B0S                                | COM4D1S          | COM4D0S        | FOC4D                              | PWM4D           |      |

| (0xC2)           | TCCR4C          |          |          |           |                                        |                  |                |                                    |                 |      |

| (0xC1)           | TCCR4B          | PWM4X    | PSR4     | DTPS41    | DTPS40                                 | CS43             | CS42           | CS41                               | CS40            |      |

| . ,              |                 |          |          |           | DTPS40<br>COM4B0                       | CS43<br>FOC4A    | FOC4B          | CS41<br>PWM4A<br>ner/Counter4 High | PWM4B           |      |

| Address          | Name     | Bit 7      | Bit 6      | Bit 5           | Bit 4               | Bit 3              | Bit 2       | Bit 1  | Bit 0  | Page |

|------------------|----------|------------|------------|-----------------|---------------------|--------------------|-------------|--------|--------|------|

| (0xBE)           | TCNT4    |            |            |                 | er/Counter4 - Co    |                    |             |        |        |      |

| (0xBD)           | TWAMR    | TWAM6      | TWAM5      | TWAM4           | TWAM3               | TWAM2              | TWAM1       | TWAM0  | -      |      |

| (0xBC)           | TWCR     | TWINT      | TWEA       | TWSTA           | TWSTO               | TWWC               | TWEN        | -      | TWIE   |      |

| (0xBB)           | TWDR     |            |            | mem             |                     | erface Data Regis  |             |        |        |      |

| (0xBA)           | TWAR     | TWA6       | TWA5       | TWA4            | TWA3                | TWA2               | TWA1        | TWA0   | TWGCE  |      |

| (0xB9)           | TWSR     | TWS7       | TWS6       | TWS5            | TWS4                | TWS3               | -           | TWPS1  | TWPS0  |      |

| (0xB8)           | TWBR     |            |            |                 | -wire Serial Interf |                    | ister       |        |        |      |

| (0xB7)           | Reserved | -          | -          | -               | -wire Genarinten    | -                  | -           | -      | -      |      |

| (0xB6)           | Reserved | -          |            |                 |                     |                    |             |        |        |      |

| (0xB5)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xB4)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xB3)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xB2)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xB1)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xB0)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xAF)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xAE)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xAD)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xAC)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xAB)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xAA)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xA9)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xA8)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xA0)<br>(0xA7) | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xA6)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xA5)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xA4)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xA3)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xA2)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xA1)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0xA0)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0x9F)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0x9E)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0x9D)           | OCR3CH   |            | 1          | Timer/Co        | unter3 - Output C   | ompare Register    | C High Byte | 1      |        |      |

| (0x9C)           | OCR3CL   |            |            |                 | unter3 - Output C   |                    | • •         |        |        |      |

| (0x9B)           | OCR3BH   |            |            |                 | unter3 - Output C   |                    |             |        |        |      |

| (0x9A)           | OCR3BL   |            |            |                 | unter3 - Output C   |                    |             |        |        |      |

| (0x99)           | OCR3AH   |            |            | Timer/Co        | unter3 - Output C   | ompare Register    | A High Byte |        |        |      |

| (0x98)           | OCR3AL   |            |            | Timer/Co        | unter3 - Output C   | ompare Register    | A Low Byte  |        |        |      |

| (0x97)           | ICR3H    |            |            | Timer/          | Counter3 - Input (  | Capture Register   | High Byte   |        |        |      |

| (0x96)           | ICR3L    |            |            | Timer/          | Counter3 - Input (  | Capture Register   | Low Byte    |        |        |      |

| (0x95)           | TCNT3H   |            |            | Tim             | er/Counter3 - Cou   | inter Register Hig | jh Byte     |        |        |      |

| (0x94)           | TCNT3L   |            |            | Tim             | er/Counter3 - Co    | unter Register Lo  | w Byte      |        |        |      |

| (0x93)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0x92)           | TCCR3C   | FOC3A      | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0x91)           | TCCR3B   | ICNC3      | ICES3      | -               | WGM33               | WGM32              | CS32        | CS31   | CS30   |      |

| (0x90)           | TCCR3A   | COM3A1     | COM3A0     | COM3B1          | COM3B0              | COM3C1             | COM3C0      | WGM31  | WGM30  |      |

| (0x8F)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0x8E)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0x8D)           | OCR1CH   |            |            | Timer/Co        | unter1 - Output C   | ompare Register    | C High Byte |        |        |      |

| (0x8C)           | OCR1CL   |            |            | Timer/Co        | unter1 - Output C   | ompare Register    | C Low Byte  |        |        |      |

| (0x8B)           | OCR1BH   |            |            | Timer/Co        | unter1 - Output C   | ompare Register    | B High Byte |        |        |      |

| (0x8A)           | OCR1BL   |            |            | Timer/Co        | unter1 - Output C   | ompare Register    | B Low Byte  |        |        |      |

| (0x89)           | OCR1AH   |            |            | Timer/Co        | unter1 - Output C   | ompare Register    | A High Byte |        |        |      |

| (0x88)           | OCR1AL   |            |            | Timer/Co        | unter1 - Output C   | ompare Register    | A Low Byte  |        |        |      |

| (0x87)           | ICR1H    |            |            | Timer/          | Counter1 - Input 0  | Capture Register   | High Byte   |        |        |      |

| (0x86)           | ICR1L    |            |            |                 | Counter1 - Input (  |                    |             |        |        |      |

| (0x85)           | TCNT1H   |            |            | Tim             | er/Counter1 - Cou   | Inter Register Hig | jh Byte     |        |        |      |

| (0x84)           | TCNT1L   |            |            | Tim             | er/Counter1 - Co    | unter Register Lo  | w Byte      |        |        |      |

| (0x83)           | Reserved | -          | -          | -               | -                   | -                  | -           | -      | -      |      |

| (0x82)           | TCCR1C   | FOC1A      | FOC1B      | FOC1C           | -                   | -                  | -           | -      | -      |      |

| (0x81)           | TCCR1B   | ICNC1      | ICES1      | -               | WGM13               | WGM12              | CS12        | CS11   | CS10   |      |

| (0x80)           | TCCR1A   | COM1A1     | COM1A0     | COM1B1          | COM1B0              | COM1C1             | COM1C0      | WGM11  | WGM10  |      |

| (0x7F)           | DIDR1    | -          | -          | -               | -                   | -                  | -           | -      | AIN0D  |      |

|                  | DIDR0    | ADC7D      | ADC6D      | ADC5D           | ADC4D               | -                  | -           | ADC1D  | ADC0D  |      |

| (0x7E)           | 0.0.00   |            |            | 100100          | ADC12D              | ADC11D             | ADC10D      | ADC9D  | ADC8D  |      |

| (0x7E)<br>(0x7D) | DIDR2    | -          | -          | ADC13D          | ADCIZD              | ABOTTB             | 1.00100     | 112002 | 7.0000 |      |

|                  |          | -<br>REFS1 | -<br>REFS0 | ADC13D<br>ADLAR | MUX4                | MUX3               | MUX2        | MUX1   | MUX0   |      |

| Address                    | Name               | Bit 7      | Bit 6         | Bit 5       | Bit 4             | Bit 3                  | Bit 2         | Bit 1             | Bit 0       | Page |

|----------------------------|--------------------|------------|---------------|-------------|-------------------|------------------------|---------------|-------------------|-------------|------|

| (0x7A)                     | ADCSRA             | ADEN       | ADSC          | ADATE       | ADIF              | ADIE                   | ADPS2         | ADPS1             | ADPS0       |      |

| (0x79)                     | ADCH               |            |               |             | ADC Data Re       | gister High byte       |               |                   | 1           |      |

| (0x78)                     | ADCL               |            |               |             | ADC Data Re       | egister Low byte       |               |                   |             |      |

| (0x77)                     | Reserved           | -          | -             | -           | -                 | -                      | -             | -                 | -           |      |

| (0x76)                     | Reserved           | -          | -             | -           | -                 | -                      | -             | -                 | -           |      |

| (0x75)                     | Reserved           | -          | -             | -           | -                 | -                      | -             | -                 | -           |      |

| (0x74)                     | Reserved           | -          | -             | -           | -                 | -                      | -             | -                 | -           |      |

| (0x73)                     | Reserved           | -          | -             | -           | -                 | -                      | -             | -                 | -           |      |

| (0x72)                     | TIMSK4             | OCIE4D     | OCIE4A        | OCIE4B      | -                 | -                      | TOIE4         | -                 | -           |      |

| (0x71)                     | TIMSK3             | -          | -             | ICIE3       | -                 | OCIE3C                 | OCIE3B        | OCIE3A            | TOIE3       |      |

| (0x70)                     | Reserved           | -          | -             | -           | -                 | -                      | -             | -                 | -           |      |

| (0x6F)                     | TIMSK1             | -          | -             | ICIE1       | -                 | OCIE1C                 | OCIE1B        | OCIE1A            | TOIE1       |      |

| (0x6E)                     | TIMSK0             | -          | -             | -           | -                 | -                      | OCIE0B        | OCIE0A            | TOIE0       |      |

| (0x6D)<br>(0x6C)           | Reserved           | -          | -             | -           | -                 | -                      | -             | -                 | -           |      |

| , ,                        | Reserved<br>PCMSK0 | PCINT7     | -<br>PCINT6   | -<br>PCINT5 | -<br>PCINT4       | -<br>PCINT3            | -<br>PCINT2   | -<br>PCINT1       | PCINT0      |      |

| (0x6B)<br>(0x6A)           | EICRB              | - PCIN17   | -             | ISC61       | ISC60             | - PCINT3               | - PCIN12      | PCINTI            | PCINTU<br>- |      |

| (0x6A)<br>(0x69)           | EICRA              | ISC31      | ISC30         | ISC01       | ISC00             | ISC11                  | ISC10         | ISC01             | ISC00       |      |

| (0x68)                     | PCICR              | -          | -             | -           | -                 | -                      | -             | -                 | PCIE0       |      |

| (0x68)<br>(0x67)           | RCCTRL             | -          | -             | -           | -                 | -                      | -             | -                 | RCFREQ      |      |

| (0x66)                     | OSCCAL             |            | ļ             | <u> </u>    |                   | alibration Registe     |               | ļ                 |             |      |

| (0x65)                     | PRR1               | PRUSB      | -             | -           | PRTIM4            | PRTIM3                 | -             | -                 | PRUSART1    |      |

| (0x64)                     | PRR0               | PRTWI      | -             | PRTIM0      | -                 | PRTIM1                 | PRSPI         | -                 | PRADC       |      |

| (0x63)                     | Reserved           | -          | -             | -           | -                 | -                      | -             | -                 | -           |      |

| (0x62)                     | Reserved           | -          | -             | -           | -                 | -                      | -             | -                 | -           |      |

| (0x61)                     | CLKPR              | CLKPCE     | -             | -           | -                 | CLKPS3                 | CLKPS2        | CLKPS1            | CLKPS0      |      |

| (0x60)                     | WDTCSR             | WDIF       | WDIE          | WDP3        | WDCE              | WDE                    | WDP2          | WDP1              | WDP0        |      |

| 0x3F (0x5F)                | SREG               | I          | Т             | Н           | S                 | V                      | N             | Z                 | С           |      |

| 0x3E (0x5E)                | SPH                | SP15       | SP14          | SP13        | SP12              | SP11                   | SP10          | SP9               | SP8         |      |

| 0x3D (0x5D)                | SPL                | SP7        | SP6           | SP5         | SP4               | SP3                    | SP2           | SP1               | SP0         |      |

| 0x3C (0x5C)                | Reserved           | -          | -             | -           | -                 | -                      | -             | -                 | -           |      |

| 0x3B (0x5B)                | RAMPZ              | -          | -             | -           | -                 | -                      | -             | RAMPZ1            | RAMPZ0      |      |

| 0x3A (0x5A)                | Reserved           | -          | -             | -           | -                 | -                      | -             | -                 | -           |      |

| 0x39 (0x59)                | Reserved           | -          | -             | -           | -                 | -                      | -             | -                 | -           |      |

| 0x38 (0x58)                | Reserved           | -          | -             | -           | -                 | -                      | -             | -                 | -           |      |

| 0x37 (0x57)                | SPMCSR             | SPMIE      | RWWSB         | SIGRD       | RWWSRE            | BLBSET                 | PGWRT         | PGERS             | SPMEN<br>-  |      |

| 0x36 (0x56)<br>0x35 (0x55) | Reserved<br>MCUCR  | -<br>JTD   | -             | -           | -<br>PUD          | -                      | -             | -<br>IVSEL        | -<br>IVCE   |      |

| 0x35 (0x55)<br>0x34 (0x54) | MCUCR              | -          | -             | -<br>USBRF  | JTRF              | -<br>WDRF              | -<br>BORF     | EXTRF             | PORF        |      |

| 0x33 (0x53)                | SMCR               | -          | -             | -           | -                 | SM2                    | SM1           | SMO               | SE          |      |

| 0x32 (0x52)                | PLLFRQ             | PINMUX     | PLLUSB        | PLLTM1      | PLLTM0            | PDIV3                  | PDIV2         | PDIV1             | PDIV0       |      |

| 0.02 (0.02)                | OCDR/              | OCDR7      | OCDR6         | OCDR5       | OCDR4             | OCDR3                  | OCDR2         | OCDR1             | OCDR0       |      |

| 0x31 (0x51)                | MONDR              | 005111     | 000110        | 005110      |                   | ata Register           | 000112        | 00010             | 000110      |      |

| 0x30 (0x50)                | ACSR               | ACD        | ACBG          | ACO         | ACI               | ACIE                   | ACIC          | ACIS1             | ACIS0       |      |

| 0x2F (0x4F)                | Reserved           | -          | -             | -           | -                 | -                      | -             | -                 | -           |      |

| 0x2E (0x4E)                | SPDR               |            |               |             | SPI Dat           | ta Register            |               |                   | -           |      |

| 0x2D (0x4D)                | SPSR               | SPIF       | WCOL          | -           | -                 | -                      | -             | -                 | SPI2X       |      |

| 0x2C (0x4C)                | SPCR               | SPIE       | SPE           | DORD        | MSTR              | CPOL                   | CPHA          | SPR1              | SPR0        |      |

| 0x2B (0x4B)                | GPIOR2             |            |               | -           |                   | se I/O Register 2      |               |                   | <u> </u>    |      |

| 0x2A (0x4A)                | GPIOR1             |            |               |             | General Purpo     | se I/O Register 1      |               |                   |             |      |

| 0x29 (0x49)                | PLLCSR             | -          | -             | -           | PINDIV            | -                      | -             | PLLE              | PLOCK       |      |

| 0x28 (0x48)                | OCR0B              |            |               |             | ner/Counter0 Outp |                        |               |                   |             |      |

| 0x27 (0x47)                | OCR0A              |            |               | Tin         | ner/Counter0 Outp | 1 0                    | ister A       |                   |             |      |

| 0x26 (0x46)                | TCNT0              |            |               |             | Timer/Co          | unter0 (8 Bit)         |               |                   |             |      |

| 0x25 (0x45)                | TCCR0B             | FOC0A      | FOC0B         | -           | -                 | WGM02                  | CS02          | CS01              | CS00        |      |

| 0x24 (0x44)                | TCCR0A             | COM0A1     | COM0A0        | COM0B1      | COM0B0            | -                      | -             | WGM01             | WGM00       |      |

| 0x23 (0x43)                | GTCCR              | TSM        | -             | -           | -                 | -                      | -             | PSRASY            | PSRSYNC     |      |

| 0x22 (0x42)                | EEARH              | -          | -             | -           |                   |                        |               | s Register High B | iyte        |      |

| 0x21 (0x41)                | EEARL              |            |               |             | EEPROM Addres     | -                      | yıe           |                   |             |      |

| 0x20 (0x40)                | EEDR<br>EECR       | -          | -             | EEPM1       | EEPROM I<br>EEPM0 | Data Register<br>EERIE | EEMPE         | EEPE              | EERE        |      |

| 0x1F (0x3F)                | GPIOR0             | -          | -             | CEPIVII     |                   | Se I/O Register 0      |               | EEPE              | CERE        |      |

| 0x1E (0x3E)                | EIMSK              |            | INT6          |             | General Purpo     | -                      | INITO         |                   | INTO        |      |

| 0x1D (0x3D)<br>0x1C (0x3C) | EIMSK              | -          | IN16<br>INTF6 | -           | -                 | INT3<br>INTF3          | INT2<br>INTF2 | INT1<br>INTF1     | INTF0       |      |

| 0x1C (0x3C)<br>0x1B (0x3B) | PCIFR              | -          | IN I F6<br>-  |             | -                 | INTF3<br>-             | INTF2<br>-    | INTF1<br>-        | PCIF0       |      |

| 0x1B (0x3B)<br>0x1A (0x3A) | Reserved           | -          | -             |             | -                 | -                      | -             | -                 | -           |      |

|                            | TIFR4              | -<br>OCF4D | -<br>OCF4A    | -<br>OCF4B  | -                 | -                      | -<br>TOV4     | -                 | -           |      |

| 0x19 (0x39)                |                    |            |               |             |                   |                        |               |                   |             |      |

| Address     | Name     | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Page |

|-------------|----------|--------|--------|--------|--------|--------|--------|--------|--------|------|

| 0x17 (0x37) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x16 (0x36) | TIFR1    | -      | -      | ICF1   | -      | OCF1C  | OCF1B  | OCF1A  | TOV1   |      |

| 0x15 (0x35) | TIFR0    | -      | -      | -      | -      | -      | OCF0B  | OCF0A  | TOV0   |      |

| 0x14 (0x34) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x13 (0x33) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x12 (0x32) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x11 (0x31) | PORTF    | PORTF7 | PORTF6 | PORTF5 | PORTF4 | -      | -      | PORTF1 | PORTF0 |      |

| 0x10 (0x30) | DDRF     | DDF7   | DDF6   | DDF5   | DDF4   | -      | -      | DDF1   | DDF0   |      |

| 0x0F (0x2F) | PINF     | PINF7  | PINF6  | PINF5  | PINF4  | -      | -      | PINF1  | PINF0  |      |

| 0x0E (0x2E) | PORTE    | -      | PORTE6 | -      | -      | -      | PORTE2 | -      | -      |      |

| 0x0D (0x2D) | DDRE     | -      | DDE6   | -      | -      | -      | DDE2   | -      | -      |      |

| 0x0C (0x2C) | PINE     | -      | PINE6  | -      | -      | -      | PINE2  | -      | -      |      |

| 0x0B (0x2B) | PORTD    | PORTD7 | PORTD6 | PORTD5 | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 |      |

| 0x0A (0x2A) | DDRD     | DDD7   | DDD6   | DDD5   | DDD4   | DDD3   | DDD2   | DDD1   | DDD0   |      |

| 0x09 (0x29) | PIND     | PIND7  | PIND6  | PIND5  | PIND4  | PIND3  | PIND2  | PIND1  | PIND0  |      |

| 0x08 (0x28) | PORTC    | PORTC7 | PORTC6 | -      | -      | -      | -      | -      | -      |      |

| 0x07 (0x27) | DDRC     | DDC7   | DDC6   | -      | -      | -      | -      | -      | -      |      |

| 0x06 (0x26) | PINC     | PINC7  | PINC6  | -      | -      | -      | -      | -      | -      |      |

| 0x05 (0x25) | PORTB    | PORTB7 | PORTB6 | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 |      |

| 0x04 (0x24) | DDRB     | DDB7   | DDB6   | DDB5   | DDB4   | DDB3   | DDB2   | DDB1   | DDB0   |      |

| 0x03 (0x23) | PINB     | PINB7  | PINB6  | PINB5  | PINB4  | PINB3  | PINB2  | PINB1  | PINB0  |      |

| 0x02 (0x22) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x01 (0x21) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x00 (0x20) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

- Note: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

- 2. I/O registers within the address range \$00 \$1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions.

- 3. Some of the status flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate on all bits in the I/O register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

- 4. When using the I/O specific commands IN and OUT, the I/O addresses \$00 \$3F must be used. When addressing I/O registers as data space using LD and ST instructions, \$20 must be added to these addresses. The ATmega16U4/ATmega32U4 is a complex microcontroller with more peripheral units than can be supported within the 64 location reserved in Opcode for the IN and OUT instructions. For the Extended I/O space from \$60 \$1FF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

# 5. Instruction Set Summary

| Mnemonics | Operands  | Description                                 | Operation                                                                                | Flags      | #Clocks |

|-----------|-----------|---------------------------------------------|------------------------------------------------------------------------------------------|------------|---------|

|           | ARITHMETI | C AND LOGIC INSTRUCTIONS                    |                                                                                          | 1          | I       |

| ADD       | Rd, Rr    | Add two Registers                           | $Rd \leftarrow Rd + Rr$                                                                  | Z,C,N,V,H  | 1       |

| ADC       | Rd, Rr    | Add with Carry two Registers                | $Rd \leftarrow Rd + Rr + C$                                                              | Z,C,N,V,H  | 1       |

| ADIW      | Rdl,K     | Add Immediate to Word                       | $Rdh:Rdl \leftarrow Rdh:Rdl + K$                                                         | Z,C,N,V,S  | 2       |

| SUB       | Rd, Rr    | Subtract two Registers                      | $Rd \leftarrow Rd - Rr$                                                                  | Z,C,N,V,H  | 1       |

| SUBI      | Rd, K     | Subtract Constant from Register             | $Rd \leftarrow Rd - K$                                                                   | Z,C,N,V,H  | 1       |

| SBC       | Rd, Rr    | Subtract with Carry two Registers           | $Rd \leftarrow Rd - Rr - C$                                                              | Z,C,N,V,H  | 1       |

| SBCI      | Rd, K     | Subtract with Carry Constant from Reg.      | $Rd \leftarrow Rd - K - C$                                                               | Z,C,N,V,H  | 1       |

| SBIW      | Rdl,K     | Subtract Immediate from Word                | Rdh:RdI ← Rdh:RdI - K                                                                    | Z,C,N,V,S  | 2       |

| AND       | Rd, Rr    | Logical AND Registers                       | $Rd \leftarrow Rd \bullet Rr$                                                            | Z,N,V      | 1       |

| ANDI      | Rd, K     | Logical AND Register and Constant           | $Rd \leftarrow Rd \bullet K$                                                             | Z,N,V      | 1       |

| OR        | Rd, Rr    | Logical OR Registers                        | $Rd \leftarrow Rd \lor Rr$                                                               | Z,N,V      | 1       |

| ORI       | Rd, K     | Logical OR Register and Constant            | $Rd \leftarrow Rd \lor K$                                                                | Z,N,V      | 1       |

| EOR       | Rd, Rr    | Exclusive OR Registers                      | $Rd \leftarrow Rd \oplus Rr$                                                             | Z,N,V      | 1       |

| COM       | Rd        | One's Complement                            | $Rd \leftarrow 0xFF - Rd$                                                                | Z,C,N,V    | 1       |

| NEG       | Rd        | Two's Complement                            | Rd ← 0x00 – Rd                                                                           | Z,C,N,V,H  | 1       |

| SBR       | Rd,K      | Set Bit(s) in Register                      | $Rd \leftarrow Rd \lor K$                                                                | Z,N,V      | 1       |

| CBR       | Rd,K      | Clear Bit(s) in Register                    | $Rd \leftarrow Rd \bullet (0xFF - K)$                                                    | Z,N,V      | 1       |

| INC       | Rd        | Increment                                   | $Rd \leftarrow Rd + 1$                                                                   | Z,N,V      | 1       |

| DEC       | Rd        | Decrement                                   | $Rd \leftarrow Rd - 1$                                                                   | Z,N,V      | 1       |

| TST       | Rd        | Test for Zero or Minus                      | Rd ← Rd • Rd                                                                             | Z,N,V      | 1       |

| CLR       | Rd        | Clear Register                              | $Rd \leftarrow Rd \oplus Rd$                                                             | Z,N,V      | 1       |

| SER       | Rd        | Set Register                                | Rd ← 0xFF                                                                                | None       | 1       |

| MUL       | Rd, Rr    | Multiply Unsigned                           | $R1:R0 \leftarrow Rd \times Rr$                                                          | Z,C        | 2       |

| MULS      | Rd, Rr    | Multiply Signed                             | $R1:R0 \leftarrow Rd \times Rr$                                                          | Z,C        | 2       |

| MULSU     | Rd, Rr    | Multiply Signed with Unsigned               | R1:R0 $\leftarrow$ Rd x Rr                                                               | Z,C        | 2       |

| FMUL      | Rd, Rr    | Fractional Multiply Unsigned                | R1:R0 ← (Rd x Rr) << 1                                                                   | Z,C        | 2       |

| FMULS     | Rd, Rr    | Fractional Multiply Signed                  | $R1:R0 \leftarrow (Rd \times Rr) << 1$                                                   | Z,C        | 2       |

|           | Rd, Rr    |                                             |                                                                                          | Z,C        | 2       |

| FMULSU    |           | Fractional Multiply Signed with Unsigned    | R1:R0 ← (Rd x Rr) << 1                                                                   | 2,0        | Ζ       |

| 5 11 15   |           | ANCH INSTRUCTIONS                           |                                                                                          |            | -       |

| RJMP      | k         | Relative Jump                               | $PC \leftarrow PC + k + 1$                                                               | None       | 2       |

| IJMP      |           | Indirect Jump to (Z)                        | $\frac{PC \leftarrow Z}{PC \leftarrow (EIND:Z)}$                                         | None       | 2       |

| EIJMP     |           | Extended Indirect Jump to (Z)               | . ,                                                                                      | None       | 2       |

| JMP       | k         | Direct Jump                                 | PC ← k                                                                                   | None       | 3       |

| RCALL     | k         | Relative Subroutine Call                    | $PC \leftarrow PC + k + 1$                                                               | None       | 4       |

| ICALL     |           | Indirect Call to (Z)                        |                                                                                          | None       | 4       |

| EICALL    |           | Extended Indirect Call to (Z)               | $PC \leftarrow (EIND:Z)$                                                                 | None       | 4       |

| CALL      | k         | Direct Subroutine Call                      | $PC \leftarrow k$                                                                        | None       | 5       |

| RET       |           | Subroutine Return                           | $PC \leftarrow STACK$                                                                    | None       | 5       |

| RETI      |           | Interrupt Return                            | $PC \gets STACK$                                                                         | 1          | 5       |

| CPSE      | Rd,Rr     | Compare, Skip if Equal                      | if $(Rd = Rr) PC \leftarrow PC + 2 \text{ or } 3$                                        | None       | 1/2/3   |

| CP        | Rd,Rr     | Compare                                     | Rd – Rr                                                                                  | Z, N,V,C,H | 1       |

| CPC       | Rd,Rr     | Compare with Carry                          | Rd - Rr - C                                                                              | Z, N,V,C,H | 1       |

| CPI       | Rd,K      | Compare Register with Immediate             | Rd – K                                                                                   | Z, N,V,C,H | 1       |

| SBRC      | Rr, b     | Skip if Bit in Register Cleared             | if (Rr(b)=0) PC $\leftarrow$ PC + 2 or 3                                                 | None       | 1/2/3   |

| SBRS      | Rr, b     | Skip if Bit in Register is Set              | if $(Rr(b)=1) PC \leftarrow PC + 2 \text{ or } 3$                                        | None       | 1/2/3   |

| SBIC      | P, b      | Skip if Bit in I/O Register Cleared         | if (P(b)=0) PC $\leftarrow$ PC + 2 or 3                                                  | None       | 1/2/3   |

| SBIS      | P, b      | Skip if Bit in I/O Register is Set          | if (P(b)=1) PC $\leftarrow$ PC + 2 or 3                                                  | None       | 1/2/3   |

| BRBS      | s, k      | Branch if Status Flag Set                   | if (SREG(s) = 1) then $PC \leftarrow PC+k + 1$                                           | None       | 1/2     |

| BRBC      | s, k      | Branch if Status Flag Cleared               | if (SREG(s) = 0) then $PC \leftarrow PC+k + 1$                                           | None       | 1/2     |

| BREQ      | k         | Branch if Equal                             | if (Z = 1) then PC $\leftarrow$ PC + k + 1                                               | None       | 1/2     |

| BRNE      | k         | Branch if Not Equal                         | if (Z = 0) then PC $\leftarrow$ PC + k + 1                                               | None       | 1/2     |

| BRCS      | k         | Branch if Carry Set                         | if (C = 1) then PC $\leftarrow$ PC + k + 1                                               | None       | 1/2     |

| BRCC      | k         | Branch if Carry Cleared                     | if (C = 0) then PC $\leftarrow$ PC + k + 1                                               | None       | 1/2     |

| BRSH      | k         | Branch if Same or Higher                    | if (C = 0) then PC $\leftarrow$ PC + k + 1                                               |            | 1/2     |

| BRLO      | k         | Branch if Same of Figher<br>Branch if Lower |                                                                                          | None       | 1/2     |

|           |           |                                             | if (C = 1) then PC $\leftarrow$ PC + k + 1<br>if (N = 1) then PC $\leftarrow$ PC + k + 1 | None       |         |

| BRMI      | k         | Branch if Minus                             | if (N = 1) then PC $\leftarrow$ PC + k + 1<br>if (N = 0) then PC $\leftarrow$ PC + k + 1 | None       | 1/2     |

| BRPL      | k         | Branch if Plus                              | if (N = 0) then PC $\leftarrow$ PC + k + 1                                               | None       | 1/2     |

| BRGE      | k         | Branch if Greater or Equal, Signed          | if $(N \oplus V = 0)$ then PC $\leftarrow$ PC + k + 1                                    | None       | 1/2     |

| BRLT      | k         | Branch if Less Than Zero, Signed            | if $(N \oplus V= 1)$ then PC $\leftarrow$ PC + k + 1                                     | None       | 1/2     |

| BRHS      | k         | Branch if Half Carry Flag Set               | if (H = 1) then PC $\leftarrow$ PC + k + 1                                               | None       | 1/2     |

| BRHC      | k         | Branch if Half Carry Flag Cleared           | if (H = 0) then PC $\leftarrow$ PC + k + 1                                               | None       | 1/2     |

| BRTS      | k         | Branch if T Flag Set                        | if (T = 1) then PC $\leftarrow$ PC + k + 1                                               | None       | 1/2     |

|           |           | Drench if T Flow Cleaned                    | if (T = 0) then PC $\leftarrow$ PC + k + 1                                               | None       | 1/2     |

| BRTC      | k         | Branch if T Flag Cleared                    | $\Pi(I=0) \Pi \Theta I F O \leftarrow F O + K + I$                                       | None       | 1/2     |

| Mnemonics  | Operands        | Description                                      | Operation                                                          | Flags        | #Clocks |

|------------|-----------------|--------------------------------------------------|--------------------------------------------------------------------|--------------|---------|

| BRVC       | k               | Branch if Overflow Flag is Cleared               | if (V = 0) then PC $\leftarrow$ PC + k + 1                         | None         | 1/2     |

| BRIE       | k               | Branch if Interrupt Enabled                      | if $(I = 1)$ then PC $\leftarrow$ PC + k + 1                       | None         | 1/2     |

| BRID       | k               | Branch if Interrupt Disabled                     | if (I = 0) then PC $\leftarrow$ PC + k + 1                         | None         | 1/2     |

|            | BIT AN          | D BIT-TEST INSTRUCTIONS                          |                                                                    |              |         |

| SBI        | P,b             | Set Bit in I/O Register                          | I/O(P,b) ← 1                                                       | None         | 2       |

| CBI        | P,b             | Clear Bit in I/O Register                        | I/O(P,b) ← 0                                                       | None         | 2       |

| LSL        | Rd              | Logical Shift Left                               | $Rd(n+1) \leftarrow Rd(n), Rd(0) \leftarrow 0$                     | Z,C,N,V      | 1       |

| LSR        | Rd              | Logical Shift Right                              | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0$                     | Z,C,N,V      | 1       |

| ROL        | Rd              | Rotate Left Through Carry                        | $Rd(0) \leftarrow C, Rd(n+1) \leftarrow Rd(n), C \leftarrow Rd(7)$ | Z,C,N,V      | 1       |

| ROR        | Rd              | Rotate Right Through Carry                       | $Rd(7) \leftarrow C, Rd(n) \leftarrow Rd(n+1), C \leftarrow Rd(0)$ | Z,C,N,V      | 1       |

| ASR        | Rd              | Arithmetic Shift Right                           | $Rd(n) \leftarrow Rd(n+1), n=06$                                   | Z,C,N,V      | 1       |

| SWAP       | Rd              | Swap Nibbles                                     | $Rd(30) \leftarrow Rd(74), Rd(74) \leftarrow Rd(30)$               | None         | 1       |

| BSET       | S               | Flag Set                                         | SREG(s) ← 1                                                        | SREG(s)      | 1       |

| BCLR       | S Da h          | Flag Clear                                       | $\frac{SREG(s) \leftarrow 0}{T \leftarrow Pr(b)}$                  | SREG(s)      | 1       |

| BST<br>BLD | Rr, b           | Bit Store from Register to T                     | $T \leftarrow Rr(b)$                                               | T            | 1       |

| SEC        | Rd, b           | Bit load from T to Register<br>Set Carry         | Rd(b) ← T       C ← 1                                              | None<br>C    | 1       |

| CLC        |                 | Clear Carry                                      |                                                                    | c            | 1       |

| SEN        |                 | Set Negative Flag                                | N ← 1                                                              | N            | 1       |

| CLN        |                 | Clear Negative Flag                              | N ← 0                                                              | N            | 1       |

| SEZ        |                 | Set Zero Flag                                    | Z ← 1                                                              | z            | 1       |

| CLZ        |                 | Clear Zero Flag                                  | $Z \leftarrow 0$                                                   | Z            | 1       |

| SEI        |                 | Global Interrupt Enable                          |                                                                    |              | 1       |

| CLI        |                 | Global Interrupt Disable                         | 1 ← 0                                                              | 1            | 1       |

| SES        |                 | Set Signed Test Flag                             | S ← 1                                                              | S            | 1       |

| CLS        |                 | Clear Signed Test Flag                           | S ← 0                                                              | S            | 1       |

| SEV        |                 | Set Twos Complement Overflow.                    | V ← 1                                                              | V            | 1       |

| CLV        |                 | Clear Twos Complement Overflow                   | $V \leftarrow 0$                                                   | V            | 1       |

| SET        |                 | Set T in SREG                                    | T ← 1                                                              | Т            | 1       |

| CLT        |                 | Clear T in SREG                                  | T ← 0                                                              | Т            | 1       |

| SEH        |                 | Set Half Carry Flag in SREG                      | H ← 1                                                              | Н            | 1       |

| CLH        |                 | Clear Half Carry Flag in SREG                    | H ← 0                                                              | Н            | 1       |

|            | DATA            | TRANSFER INSTRUCTIONS                            |                                                                    |              |         |

| MOV        | Rd, Rr          | Move Between Registers                           | Rd ← Rr                                                            | None         | 1       |

| MOVW       | Rd, Rr          | Copy Register Word                               | Rd+1:Rd ← Rr+1:Rr                                                  | None         | 1       |

| LDI        | Rd, K           | Load Immediate                                   | $Rd \leftarrow K$                                                  | None         | 1       |

| LD         | Rd, X           | Load Indirect                                    | $Rd \leftarrow (X)$                                                | None         | 2       |

| LD         | Rd, X+          | Load Indirect and Post-Inc.                      | $Rd \leftarrow (X), X \leftarrow X + 1$                            | None         | 2       |

| LD         | Rd, - X         | Load Indirect and Pre-Dec.                       | $X \leftarrow X - 1, Rd \leftarrow (X)$                            | None         | 2       |

| LD         | Rd, Y           | Load Indirect                                    | $Rd \leftarrow (Y)$                                                | None         | 2       |

| LD<br>LD   | Rd, Y+          | Load Indirect and Post-Inc.                      | $\frac{Rd \leftarrow (Y), Y \leftarrow Y + 1}{Y \leftarrow Y - 1}$ | None         | 2       |

| LDD        | Rd, - Y         | Load Indirect and Pre-Dec.                       | $Y \leftarrow Y - 1, Rd \leftarrow (Y)$                            | None         | 2       |

| LDD        | Rd,Y+q<br>Rd, Z | Load Indirect with Displacement<br>Load Indirect | $\frac{Rd \leftarrow (Y + q)}{Rd \leftarrow (Z)}$                  | None<br>None | 2       |

| LD         | Rd, Z+          | Load Indirect and Post-Inc.                      | $Rd \leftarrow (Z), Z \leftarrow Z+1$                              | None         | 2       |

| LD         | Rd, -Z          | Load Indirect and Pre-Dec.                       | $Z \leftarrow Z - 1, Rd \leftarrow (Z)$                            | None         | 2       |

| LDD        | Rd, Z+q         | Load Indirect with Displacement                  | $Rd \leftarrow (Z + q)$                                            | None         | 2       |

| LDS        | Rd, k           | Load Direct from SRAM                            | $Rd \leftarrow (k)$                                                | None         | 2       |

| ST         | X, Rr           | Store Indirect                                   | (X) ← Rr                                                           | None         | 2       |

| ST         | X+, Rr          | Store Indirect and Post-Inc.                     | $(X) \leftarrow \operatorname{Rr}, X \leftarrow X + 1$             | None         | 2       |

| ST         | - X, Rr         | Store Indirect and Pre-Dec.                      | $X \leftarrow X - 1, (X) \leftarrow Rr$                            | None         | 2       |

| ST         | Y, Rr           | Store Indirect                                   | $(Y) \leftarrow Rr$                                                | None         | 2       |

| ST         | Y+, Rr          | Store Indirect and Post-Inc.                     | $(Y) \leftarrow Rr, Y \leftarrow Y + 1$                            | None         | 2       |

| ST         | - Y, Rr         | Store Indirect and Pre-Dec.                      | $Y \leftarrow Y - 1, (Y) \leftarrow Rr$                            | None         | 2       |